英特尔Foveros 3D封装技术

随着特征缩放到达物理极限,半导体行业开始研究后摩尔技术。在此领域,无论光刻技术节点,还是7纳米传统集成电路、28纳米射频集成电路,多芯片封装对于在小形状因子中集成多种功能是至关重要的。所有这些都必须确保低成本并在短时间内上市。以此来看,Intel已经开发了几种互连技术以实现小芯片(chiplet)的异构集成。早在2018年,人们就在英特尔处理器上看到了这一技术的雏形,当时称为嵌入式多芯片互连桥(EMiB)。今天,英特尔展示了另一种在处理器中使用有源转接板和Foveros技术进行芯片互连的方案。

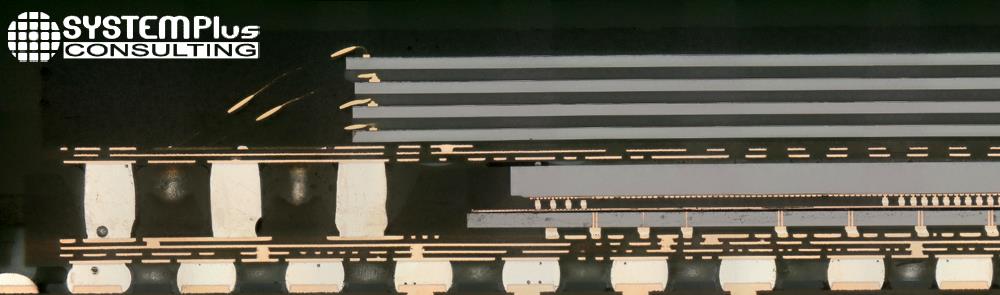

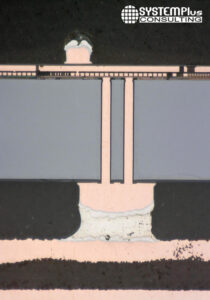

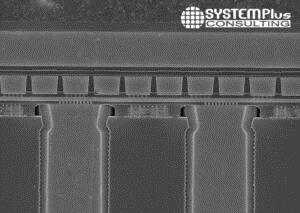

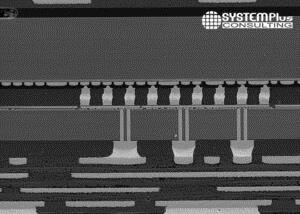

Foveros允许3D面对面(F-F)堆叠,通过使用硅通孔(TSV)在有源转接板上集成不同类型的器件。转接板作为不同小芯片之间的桥梁。它也包括低功率器件,如输入/输出(I/O)连接和高性能逻辑功率传输。

本报告分析的产品为英特尔Core i5-L16G7,特色是采用了英特尔的混合封装技术。该技术依赖于Foveros F-F芯片堆叠和PoP结构。该设计旨在将10nm运算芯片与SK Hynix LPDDR4 DRAM集成在一个PoP架构的封装体中。该方案降低了功耗并提高了核心性能,同时降低形状因子和Z高度,以适应超级移动应用。在该结构中,采用Foveros F-F技术和Via-Middle TSV工艺将10nm的运算芯片与22nm转接板直接互连,这样就可以方便地将功率传输到处理器芯片上。

关于Intel Foveros 3D Packaging Technology

本报告对英特尔 Core i5-L16G7处理器进行了详尽分析,全面调研了英特尔混合封装技术,还分析了集成在封装体内的LPDDR4X DRAM芯片。最后,它包含了完整的成本分析和器件销售价格预估,并与台积电的CoWoS技术进行比较。

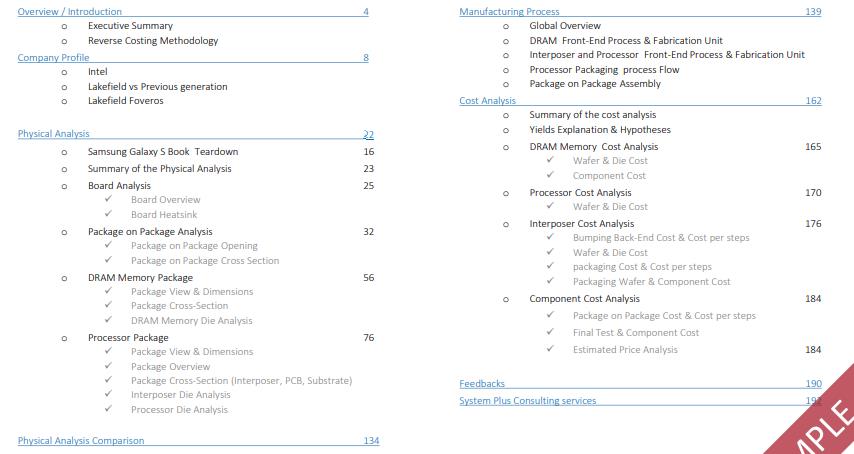

报告目录

相关报告

Fan-Out Packaging Processes Comparison 2020

Advanced System-in-Package Technology in Apple’s AirPods Pro

Advanced packaging technology in the Apple Watch Series 4’s System-in-Package

Status of the Advanced Packaging Industry 2020

Advanced Packaging Quarterly Market Monitor

(x)PU: High-End CPU and GPU for Datacenter Applications 2020

购买方式

如需样刊或购买报告,请联系华进战略部:0510-66679351 Xiaoyunzhang@ncap-cn.com

以上图文译自Yole Développement的Intel Foveros 3D Packaging Technology,原文请参考:

https://www.i-micronews.com/products/intel-foveros-3d-packaging-technology/

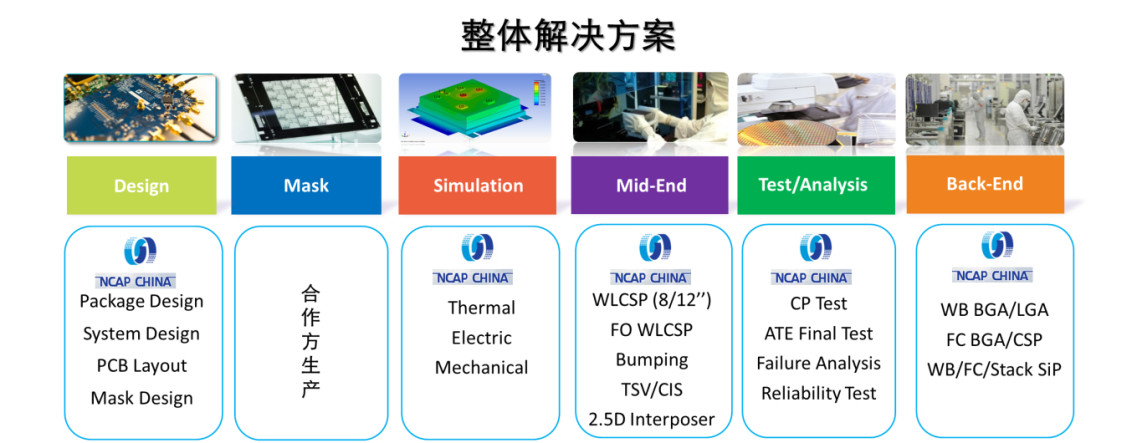

关于华进

华进半导体于2012年9月在无锡新区正式注册成立,开展系统级封装/集成先导技术研究,研发2.5D/3D TSV互连及集成关键技术(包括TSV制造、凸点制造、TSV背露、芯片堆叠等),为产业界提供系统解决方案。同时将开展多种晶圆级高密度封装工艺(包括WLCSP/Fan-out)与SiP产品应用的研发与大规模量产,以及与封装技术相关的材料和设备的验证与研发。

网址:www.ncap-cn.com

微信:NCAP-CN

*转载须知*

文首注明:转载自华进半导体(ID:NCAP-CN)

阅读原文处,请插入华进半导体原文链接

未经同意,不可修改文章内容

若未遵守上述规则,将按侵权处理

中文

中文

English

English 苏公网安备 32021402001899号

苏公网安备 32021402001899号